# Letters

## Corrections to “A Generalized Theory of Tapered Transmission Line Matching Transformers and Asymmetric Couplers Supporting Non-TEM Modes”

Protag Pramanick and Prakash Bhartia

The above paper<sup>1</sup> contains four typographical errors. Equation (18) should read

$$F(\bar{u}) = \ln(\bar{Z}_L) \frac{\cos[\pi\sqrt{\bar{u}^2 - \bar{u}_0^2}]}{\cosh(\pi\bar{u}_0)}.$$

Equation (23) should read

$$\Phi\left(\frac{\theta}{\pi\bar{u}_0}, \pi\bar{u}_0\right) = \frac{1}{\pi\bar{u}_0} \int_0^\theta \frac{I_1\left[\pi\bar{u}_0 \sqrt{1 - \left(\frac{x}{\pi\bar{u}_0}\right)^2}\right]}{\pi\bar{u}_0 \sqrt{1 - \left(\frac{x}{\pi\bar{u}_0}\right)^2}} dx.$$

In equation (28) one should read

$$b_n = \frac{0.5x(1-x^2)^n + 2nb_{n+1}}{(2n+1)}.$$

In equation (34) one should read

$$N = (4/\pi)(b/a)(1 + 0.2\sqrt{b/a}).$$

The authors are thankful to J. C. Coetze of the Department of Electrical Engineering, University of Pretoria, South Africa, for pointing out these errors.

Manuscript received September 18, 1990.

P. Pramanick is with COM DEV Ltd., 155 Sheldon Drive, Cambridge, Ontario, N1R 7H6 Canada.

P. Bhartia is with the Underwater Acoustics Division, DRE, Atlantic, 9 Groove Street, Dartmouth, Nova Scotia, B2Y 3Z7 Canada.

IEEE Log Number 9041072.

<sup>1</sup>P. Pramanick and P. Bhartia, *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1184–1191, Aug. 1989.

## Comments on “Parallel Processing Application to Nonlinear Microwave Network Design”

B. Ray Sperber

In the above paper<sup>1</sup> Fig. 6 shows a speedup curve for a network of Transputer processors and apparently is a plot of the data given there in Table I. Could the authors please explain

Manuscript received July 11, 1990.

The author is with SES, Chateau de Betzdorf, L-6815 Betzdorf, Luxembourg.

IEEE Log Number 9041071.

<sup>1</sup>M. I. Sobhy and Y. A. R. El-Sawy, *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 2067–2073, Dec. 1989.

TABLE I

SOLUTION TIME FOR AMPLIFIER EXAMPLE USING T800 TRANSPUTERS

| Number of Transputers | Time s | Efficiency $\eta$ |

|-----------------------|--------|-------------------|

| 1                     | 1.6    |                   |

| 2                     | 1.08   | 74%               |

| 3                     | 0.85   | 63%               |

| 4                     | 1.0    | 40%               |

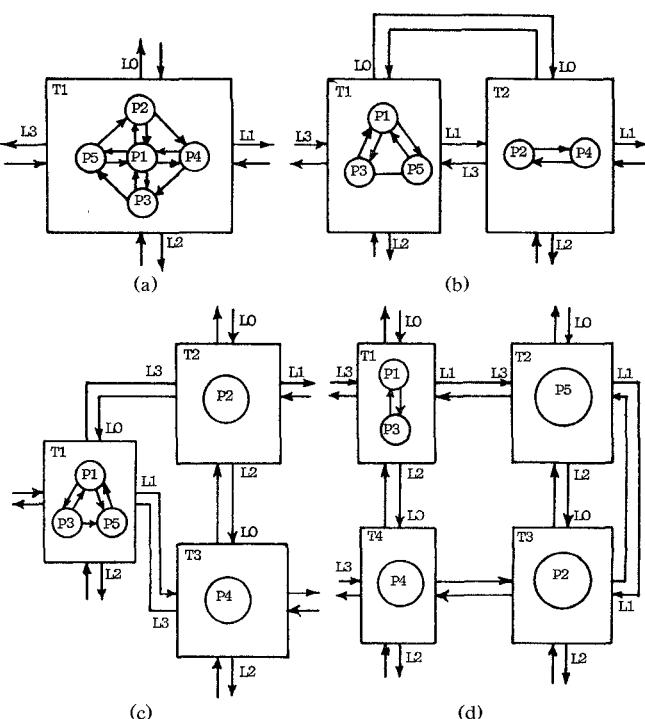

Fig. 1. Configuration of the main processes over (a) one Transputer, (b) two Transputers, (c) three Transputers, and (d) four Transputers. T1–T4 denote the Transputers, P1–P5 the processes, and L0–L3 the links.

how the data shown support their summarized result in Section IX, where they state that “the addition of more Transputers will also reduce the computational time.”

An additional aspect that is unclear is the extent to which the configuration of the Transputer network and/or the task sharing of the Transputers was different in the different cases in Fig. 6/Table I. In particular, how did the network in Fig. 5 differ for the different cases of Fig. 6/Table I? To what extent are the processes of Fig. 4 allocated to the Transputers in each of the cases of Fig. 6/Table I?

Finally, is it correct to assume that the Transputers were on commercially available mass-produced boards and that the OCCAM software used was a standard (as opposed to custom) language package? If the authors would please provide some more details on these aspects it might be of great interest to the MTT community.

The authors are to be congratulated for presenting an intriguing paper on an interesting topic.

**Reply<sup>2</sup> by M. I. Sobhy and Y. A. R. El-Sawy<sup>3</sup>**

We thank Sperber for his interest in our paper and we present the following answers to his questions.

- 1) In the nonlinear amplifier example in Section IX the time of 3.2 s was obtained by using only one T414 Transputer. The comment that "the addition of more Transputers will also reduce the computational time" is consistent with the data in Fig. 6 and Table I. The time is reduced to 2.3 s with two Transputers and to 1.8 with three. The time starts to rise again with four Transputers owing to the increase in the communication time between Transputers. These re-

sults were obtained using a very early board with T414 Transputers which did not have hardware floating point arithmetic. Table I presented here gives the times for the same example using T800 Transputers with floating point hardware and should be compared with Table I in our paper. If the circuit is to be analyzed for different frequencies or at different power levels, then each frequency or power level can be solved in parallel on a system of Transputers and the overall time should be the same as the time for only one solution.

- 2) The configurations using one to four Transputers are shown here in Fig. 1, where the processes P1-P5 are as defined in Section VII of our paper and T1-T4 are the four Transputers.

- 3) The boards used are standard boards available commercially and the OCCAM software was also a standard commercially available package.

Finally, we thank Sperber for his kind congratulations.

<sup>2</sup>Manuscript received August 29, 1990.

<sup>3</sup>The authors are with the Electronic Engineering Laboratories, University of Kent At Canterbury, Canterbury, Kent, CT2 7NT, U.K.

IEEE Log Number 9041070.